- ALL COMPUTER, ELECTRONICS AND MECHANICAL COURSES AVAILABLE…. PROJECT GUIDANCE SINCE 2004. FOR FURTHER DETAILS CALL 9443117328

Projects > ELECTRONICS > 2017 > IEEE > VLSI

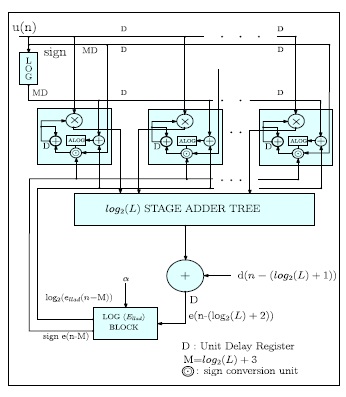

This paper presents a framework based on the logarithmic number system to implement adaptive filters with error nonlinearities in hardware. The framework is demonstrated through pipelined implementations of two recently proposed adaptive filtering algorithms based on logarithmic cost, namely, least mean logarithmic square (LMLS) and least logarithmic absolute difference (LLAD). To the best of our knowledge, the proposed architectures are the first attempts to implement both LMLS and LLAD algorithms in hardware. We derive error computing algorithms to realize the nonlinear error functions for LMLS and LLAD and map them onto hardware. We also propose a novel variable-α scheme to enhance the original LMLS algorithm and prove its robustness and suitability for VLSI implementations in practical applications. Detailed bit width and error analysis are carried out for the proposed VLSI fixed point implementations. Postlayout implementation results show that with an additional multiplier over conventional least mean square (LMS), 7-dB improvement in steady-state mean square deviation performance can be achieved and with the proposed variable-α scheme, 12-dB improvement can be achieved without compromising the convergence. We will show that LMLS can potentially replace LMS in practical applications, by demonstrating a proof-of-concept by extending the framework to transform domain adaptive filters.

Mean Mixed-Norm Adaptive Filtering, Adaptive Filtering Algorithm.

Error nonlinear adaptive algorithms can improve the performance of the LMS algorithm without sacrificing the simplicity and stability properties of LMS. As demonstrated through LMLS/LLAD algorithms, any error. Our main contributions include the following. We propose a VLSI architecture for delayed LMLS (DLMLS) algorithm, which combines the benefits of LMS and LMF and its stability is as good as the LMS algorithm. We propose a variable-α scheme to improve the steady-state MSD of the LMLS algorithm further. We propose a low-complexity VLSI architecture for delayed LLAD (DLLAD) algorithm, which combines the benefits of sign LMS and LMS in impulsive noise environments. We generalize the framework, which can be extended to other error nonlinear adaptive algorithms like QK-LMS and so on.

DLMS architecture

DLLAD architecture