- ALL COMPUTER, ELECTRONICS AND MECHANICAL COURSES AVAILABLE…. PROJECT GUIDANCE SINCE 2004. FOR FURTHER DETAILS CALL 9443117328

Projects > ELECTRONICS > 2017 > IEEE > VLSI

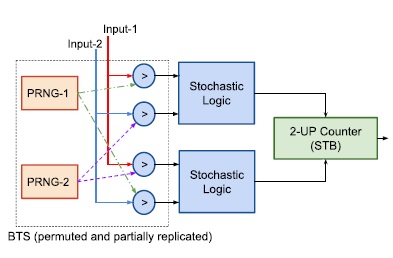

Designing reliable systems, while eschewing the high overheads of conventional fault tolerance techniques, is a critical challenge in the deeply scaled CMOS and post-CMOS era. To address this challenge, we leverage the intrinsic resilience of application domains such as multimedia, recognition, mining, search, and analytics where acceptable outputs are produced despite occasional approximate computations. We propose stochastic checkers (checkers designed using stochastic logic) as a new approach to performing error checking in an approximate manner at greatly reduced overheads. Stochastic checkers are inherently inaccurate and require long latencies for computation. To limit the loss in error coverage, as well as false positives (correct outputs flagged as erroneous), caused due to the approximate nature of stochastic checkers, we propose input permuted partial replicas of stochastic logic, which improves their accuracy with minimal increase in overheads. To address the challenge of long error detection latency, we propose progressive checking policies that provide an early decision based on a prefix of the checker’s output bitstream. This technique is further enhanced by employing progressively accurate binary-to-stochastic converters. Across a suite of error-resilient applications, we observe that stochastic checkers lead to greatly reduced overheads compared with traditional fault tolerance techniques while maintaining high coverage and very low false positives.

Stochastic Recognition.

Our contributions can be summarized as follows. We propose StoCK, an approach to design low-overhead checkers using stochastic logic for applications that can tolerate approximate computations. We propose input permuted partial replicas (IPPRs) of stochastic circuits to improve the accuracy of stochastic checkers, thereby improving both their coverage and false positive rate. We propose progressive checking policies, wherein the stochastic checker performs checks using a prefix of the output bitstream, improving error detection latency. We propose progressively accurate binary-to-stochastic (PA-BTS) converters that reduce conversion errors at lower latencies, thus further improving the effectiveness of progressive checking. We implement and evaluate stochastic error checkers for a suite of error-resilient applications and demonstrate that they can lead to very high fault coverage and very low false positives, at considerably reduced overheads compared with conventional techniques.

Stochastic checker with permuted partial replicas

Error detection latency reduction without chaining and (b) with chaining